Note that the keyboard needs to be a PS/2 keyboard with USB interface to work with the Digilent board. This method does not require a separate PC, once the bitstream has been burned to quad-spi flash. Connect a USB-keyboard and VGA compatible LCD display You should be able to see the boot program copy the boot.bin from SD to DDR RAM and then boot it. With most systems this may be done with the file manager or similar GUI program. Note: make sure the Linux image boot.bin and boot.md5 is copied to SD beforehand. Other than manually loading a Linux to the DDR RAM using the debugger, we can use the selftest program to load Linux from SD, if switch(1) is high (second from right). If you have a VGA display connected, you will see all output in both places (apart from Berkley boot loader messages). (in an on-chip BRAM) which just jumps to DDR RAM if switch(0) is high (on the right). The pre-built FPGA bitstream has a selftest program as the 1st stage bootloader opensocdebugd uart device=/dev/ttyUSB1 speed=12000000 & In this case the device is user and group only access, so you need to be a member of the group dialout to use it. Which should result in a response similar to: crw-rw- 1 root dialout 188, 1 Apr 14 16:32 /dev/ttyUSB1

#Vivado download bitstream to fpga serial

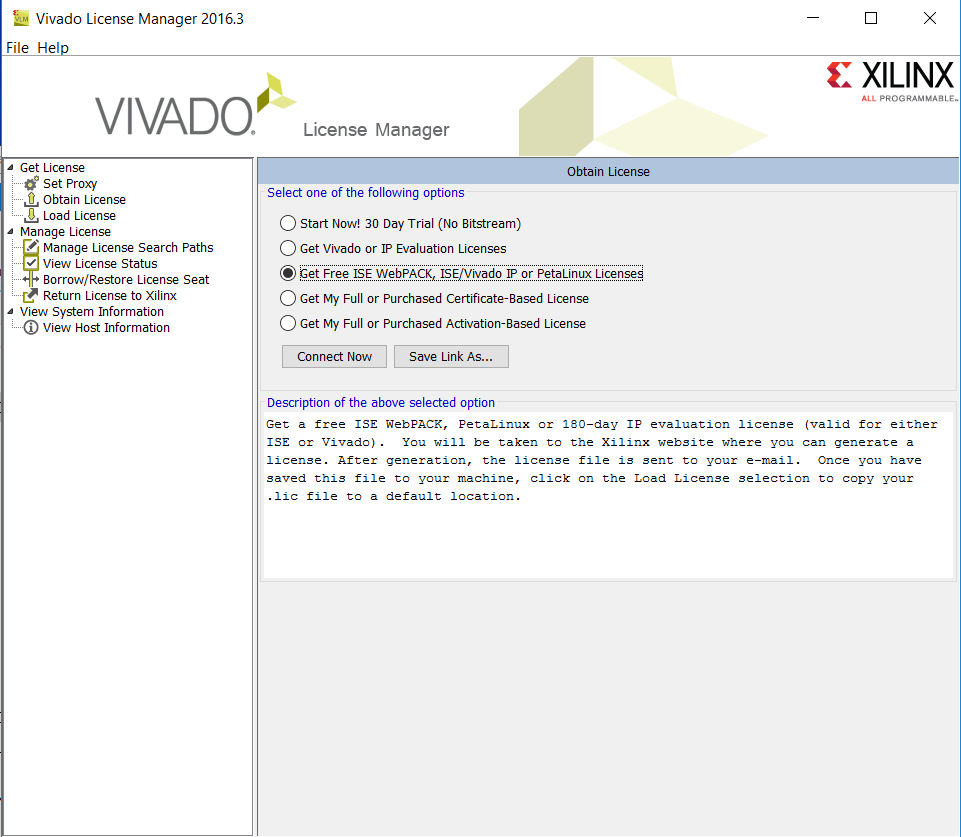

First check the available serial ports: ls -l /dev/*USB* For the first two cases, we need to open the debug daemon to load programs and connect to the UART console. There are three ways to boot a RISC-V Linux. Optional: It is helpful to check the integrity of the kernel before we load it md5sum boot.bin > boot.md5Ĭonvert the bitstream to quad-spi memory format vivado -mode batch -source $TOP/fpga/common/script/cfgmem.tcl -tclargs "xc7a100t_0" nexys4ddr_fpga.bitīurn the quad-spi memory (Ensure the MODE switch is set to QSPI) vivado -mode batch -source $TOP/fpga/common/script/program_cfgmem.tcl -tclargs "xc7a100t_0" nexys4ddr_ Linux, Busybox and Berkley bootloader (BBL) packaged in one image.ĭownload and write the bitstream curl -L > nexys4ddr_fpga.bit The tagpipe/minion/debug enabled FPGA bitstream The debug system will use the UART connection at 12 MBaud to communicate with In this final step, we want to test the debug functionality on an FPGA board.

⇡ Tutorial for the v0.4 lowRISC release Running on the FPGA

0 kommentar(er)

0 kommentar(er)